Cloud native EDA tools & pre-optimized hardware platforms

For decades, the task of creating masks for the manufacturing process has been an integral part of semiconductor manufacturing. As we move to more advanced nodes like 5nm, 3nm to 2nm, accelerating computational lithography turnaround time is instrumental in getting the chips fabricated efficiently in semiconductor manufacturing companies. 짇북꽈殮꺄역쉽 has been a pioneer in this area with advanced techniques to accelerate distributed processing in areas like supercomputers.

Our latest collaboration with NVIDIA to run 짇북꽈殮꺄역쉽 Proteus Optical Proximity Correction (OPC) software on the is just one example of how we are providing another powerful way to accelerate that process on GPUs, taking it from weeks to days.

What this means for foundries and customers using these solutions is substantially faster turnaround times to develop chips on increasingly smaller process nodes. “As applications such as AI and machine learning drive the demand for greater density from smaller chips, lithography processes need a substantial speed boost to keep up with the pace of innovation,” said Vivek Singh, vice president, Advanced Technology Group, NVIDIA. “By collaborating with 짇북꽈殮꺄역쉽, we are accelerating the massive computational workloads that currently consume tens of billions of CPU hours every year, enabling the creation of new lithography solutions and more predictability in future semiconductor technologies.”

Read on to learn more about why this collaboration is good news for semiconductor scaling―and every application demanding more performance from smaller footprints.

What Is Computational Lithography?

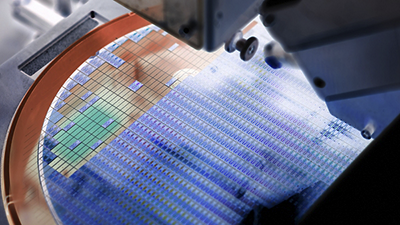

In semiconductor manufacturing, photolithography helps dictate the size of a chip’s transistors. Similar to the way that an image from a negative gets exposed onto paper during the photographic process, the photolithography process uses light to produce patterns representing a chip’s design onto a silicon wafer.

As transistor sizes shrink, the lithographic process must become more precise to transfer the patterns from the photomasks on to the wafer with greater accuracy. At very small sizes, when features are closer together, it’s generally not feasible to obtain a clean and accurate representation of the mask’s patterning on the wafer. The diffusion of the light impacts resolution, causing blurring or distortion. For example, an L-shaped pattern may actually contain other lines or shapes protruding from the perimeter. But at very small sizes, these shapes may not get printed on the wafer during the photolithographic process. As a result, important elements of the chip could be missed.

Computational lithography has emerged to compensate for any image errors that could stem from diffraction or optical, resist, and etching proximity effects. Through OPC software, the process does so by playing tricks with the light via an algorithmic and mathematical approach, along with a lot of simulation work. The process involves going through different “what if?” scenarios to find the right configuration to print a pattern with the highest accuracy possible. For example, projecting light with the right artifacts around it, such as serifs that can manipulate the light, can generate a print on the wafer that is closer to the original than without these carefully selected artifacts.

Figure 1: OPC/ILT mask, where the green lines indicate outlines of the mask features that are needed to print a simple square contact on silicon. This example illustrates the complexity in computational lithography algorithms.

Why Fast Computational Speed Is Critical for Mask Synthesis

As Moore’s law slows and the semiconductor industry approaches the limits of physics, new techniques and technologies have emerged to enable continued innovation. Nanometers will eventually make way for angstroms to deliver even greater density in much smaller form factors. At these sizes, the need for computational lithography can only grow.

Computational lithography is a resource-intensive undertaking, typically requiring massive data centers to handle the calculations and simulation runs involved. The process could take many, many hours, even when using the most powerful computers. As designers aim to pack more transistors onto their chips, further increasing the challenges of photolithography, computational workloads will only grow. The simulation aspect of computational lithography is one of the most time-consuming parts of this process. Simulation is applied to detailed models of each step in the lithographic process. With potentially millions of small tiles in a full-chip application, it’s imperative to have super-fast computational speed for mask synthesis.

To achieve the needed performance uplift, has been integrated into the 짇북꽈殮꺄역쉽 Proteus? full-chip mask synthesis solution and 짇북꽈殮꺄역쉽 Proteus ILT inverse lithography technology, and optimized to run on the . The Proteus mask synthesis solution performs full-chip proximity correction, building models for correction and analyzing proximity effects on both corrected and uncorrected IC layout patterns. The Proteus ILT solution uses inverse imaging technology to resolve challenging optimal proximity effects at advanced technology nodes, helping to identify the optimal mask shapes to print the design intent on the silicon wafer.

Rather than requiring 40,000 CPU systems under traditional configurations, the Proteus solutions running on the cuLitho platform require only 500 . All parts of the computational lithography process can run in parallel, reducing power requirements and runtimes from weeks down to days. In addition to reduced environmental impact from the data centers, the solution also enables faster simulation runs, which can improve both time to market and quality of results of the silicon.

The Path to Higher Chip Density and Yield

From smart speakers to self-driving cars, engineering ingenuity continues delivering an array of unique products that impact our everyday lives. Advancements in semiconductors―and semiconductor manufacturing technologies―are critical for every new wave of innovation.

Enhancing computational performance for lithography is a major achievement. There are also plenty of opportunities for improvements in other aspects of the process, such as modeling in mask synthesis. For example, what might be possible if AI, which is fast-becoming mainstream technology in the chip design world, could help develop better mask models that further enhance the turnaround time and quality of the silicon? With the collective brainpower in the electronics industry, there’s no telling what the next generation of chips will deliver∼and how we’ll get there.