Cloud native EDA tools & pre-optimized hardware platforms

ÁůşĎ˛ĘÖ±˛ĄżŞ˝± is a leading provider of electronic design automation solutions and services.

ÁůşĎ˛ĘÖ±˛ĄżŞ˝± is a leading provider of high-quality, silicon-proven semiconductor IP solutions for SoC designs.

ÁůşĎ˛ĘÖ±˛ĄżŞ˝± is a leading provider of hardware-assisted verification and virtualization solutions.

The Risk of Not Running Clock Domain Crossing (CDC) on your FPGA/ASIC Design

Clock Domain Crossing (CDC) failures are a leading cause of expensive respins resulting in missed design deadlines and even worse total design failure in the field.?In general, a good CDC analysis is a vital component in a robust ASIC or FPGA design flow, and a failure to do so well puts the whole development cycle at risk.?

In this session, weˇŻll discuss what CDCs are and how missing CDCs can lead to silicon failure. WeˇŻll also talk about what is meant to achieve a ˇ®CDC-cleanˇŻ design along with best practices to achieve this with minimal schedule impact. Finally, weˇŻll cover why only CDC-clean RTL may not be good enough.?Whether you already run CDC or if you just have a sneaking suspicion that you should be, this session is for you!

Why Attend? - YouˇŻll learn about the risks you may be taking without even being aware of them.?YouˇŻll also learn about common pitfalls in running CDC and how to improve an existing CDC methodology or develop a new one from scratch.

Who Should Attend? - Designers who have one or more asynchronous clock domains in their designs. Purely synchronously clocked designs do not contain clock domain crossings.

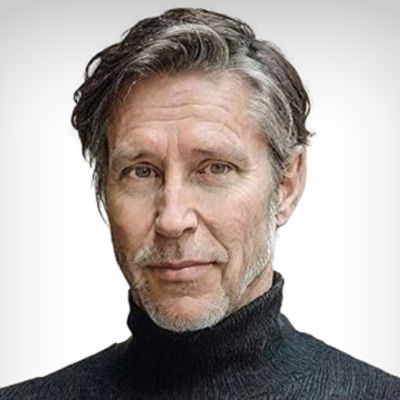

Speaker:

Oz Osborn ¨C Principal Engineer

James Osborn, better known as Oz, has worked as a field applications engineer for over 25 years, both in and out of EDA at companies including Cadence, Zycad, Packet Video and Atrenta. He's currently a Principal Engineer at ÁůşĎ˛ĘÖ±˛ĄżŞ˝±, focusing on our static tools, particularly the VC SpyGlass platform.